基于Sigrity的常规SI仿真流程(下)

上篇中介绍了通过仿真发现板中信号质量问题的过程,本篇将介绍仿真工具如何帮助工程师定位并解决问题。

02

BroadbandSpice基于S参数的TDR分析

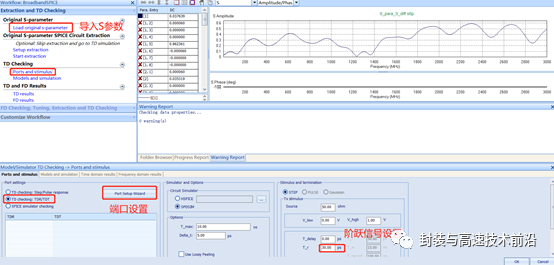

打开BroadbandSpice软件,导入S参数文件,选择Ports and stimulus:

选择TD checking:TDR/TDT流程,中间点击可进行端口设置,右边可进行阶跃信号源的参数设置,这里30ps的上升时间不用动(实际时域反射计的上升时间一般为25ps左右,设置在20-30ps均可)。

点击端口设置,打开port设置窗口:

设置差分端口,左键选择port1(差分正极),按住ctrl再选择port2(差分负极),然后右键定义为差分端口。

同样的将port5和port6定义为差分端口,这两个差分端口就是长链路的两端的端口。

下一步后,选择差分端口[1,2]为TDR端口,选择差分端口[5,6]为TDT端口。

完成端口设置。

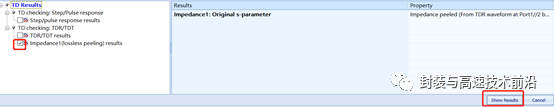

选择models and simulations,勾选原始S参数选项,点击run,运行仿真:

仿真结果选择阻抗一行进行查看:

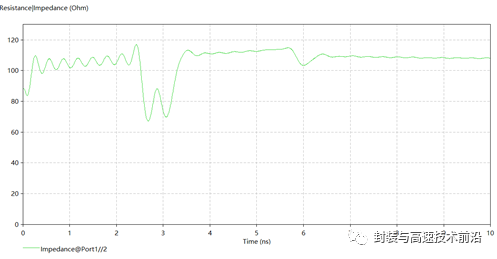

如下:

从全链路TDR阻抗结果来看,起始阶段和3ns前后出现很大的凹陷,阻抗低能达到60多欧姆,通过延时与长度的关系可以看出,第一段是芯片扇出和换层过孔带来的容性效应压低了阻抗,而中间是连接器多个过孔带来的很大的容性效应,压低了阻抗。

03

设计优化及仿真迭代验证

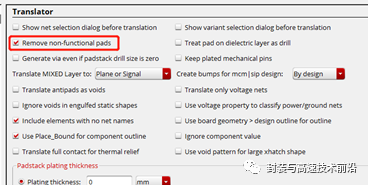

PowerSI去掉非功能焊盘

去掉非功能焊盘简便的操作就是在导入PCB文件时,勾选去掉非功能焊盘选项:

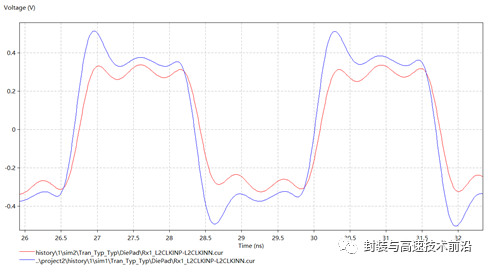

同样的模型提取流程重新提取一遍,级联S参数与时域仿真,保留与去掉非功能焊盘的时域波形对比结果如下图:

可见,优化效果很明显。

PowerSI-3DEM过孔扫描优化

打开3DEM软件,新建HSSO工程:

导入层叠模板,可以选择导入之前用于模型提取的设置好层叠的spd文件:

导入完成效果如上。

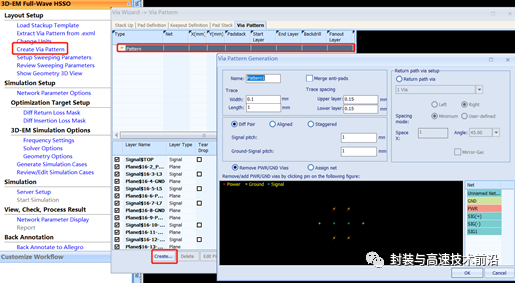

创建过孔模式,打开窗口后点击create,在generation窗口设置想要的过孔模式,扇出线宽长度、走线间距、模式、伴地孔等:

创建好过孔模式后,在下面的界面可以继续编辑过孔结构及参数,完成后点击generate生成保存过孔模式:

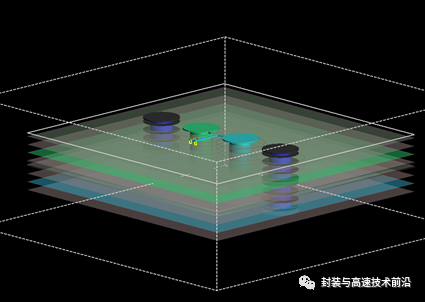

三维过孔结果如下:

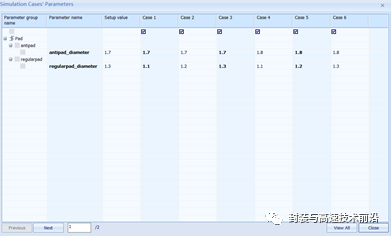

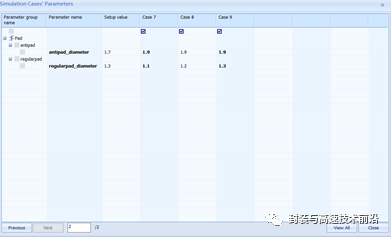

设置扫描参数,本case扫描焊盘的两个参数—焊盘大小以及反焊盘大小:

总共9种参数组合进行扫描。

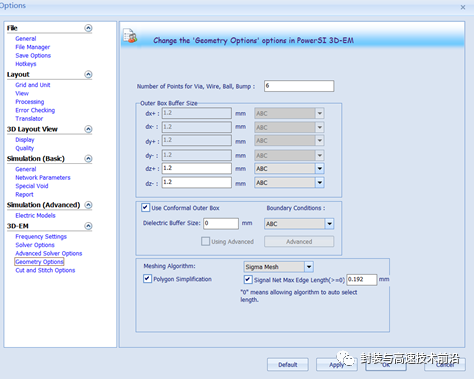

3DEM仿真相关设置:

仿真结果如下:

可见case3的结果是优秀的。

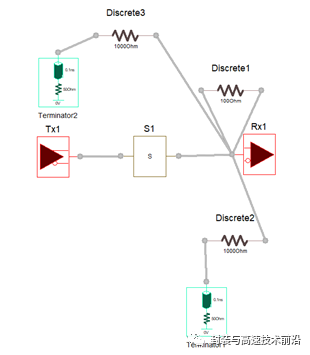

SystemSI端接what-if分析

可以在System Explorer工程环境中通过添加器件Discrete、terminal等模块来进行what-if分析:

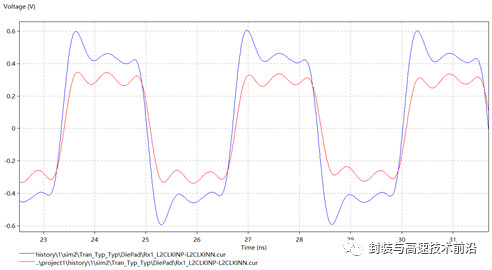

上面就是在接收端差分信号的每根线上接一个1kΩ的接地电阻,发现结果可以提高电平值,如下:

这种原理级别的what-if分析可以帮助从硬件原理上评估如何改善信号质量。

04

总结

以上只是常规的SI仿真流程,可以帮助我们从频域和时域两个角度去评估设计质量,但发现问题、定位问题、优化设计的每一项里面都有很多细节与讲究,例如何时该用3D全波电磁场工具做模型提取、仿真结果分析(S参数、波形、眼图等结果的解读)、如何指导设计修改等,这些则需要扎实的理论基础和丰富的实战经验以及功能全面的分析工具做支撑。

更多技术文章与讨论欢迎关注微信公众号:

封装与高速技术前沿

微信号 : APDtech