案例分享:射频模块仿真分析

“ 在技术革命不断深化的今天,不断增加的实际应用对系统设计提出了更高的要求,具体表现在体积的小型化、模块化和功能的集成化。这些需求也进而体现在射频系统的设计上。在现阶段,仅依靠人工计算进行的设计方式无论是在速度上还是计算的准确性上都已不再适应射频的系统设计。在产品设计初期识别、预防和改正设计错误,可以防止设计出错,这种操作模式比以往任何时候都至关重要,仿真是好的方法之一。现在高速数字电路的仿真已经走在了射频电路的前面,射频电路的设计主要还是依靠长期实践经验的积累,反复的调试,然后再作修改,设计周期过长,那么使用仿真软件来加快设计进度,缩短研发周期,提高设计准确性已成了必然的选择。”

本次案例就是一个典型的未经过仿真验证投板后测试结果不如人意的射频模块应用,所要解决的问题就是射频模块PCB板的衰减过大问题。具体介绍如下:

01

—

基本信息与问题

基本信息:

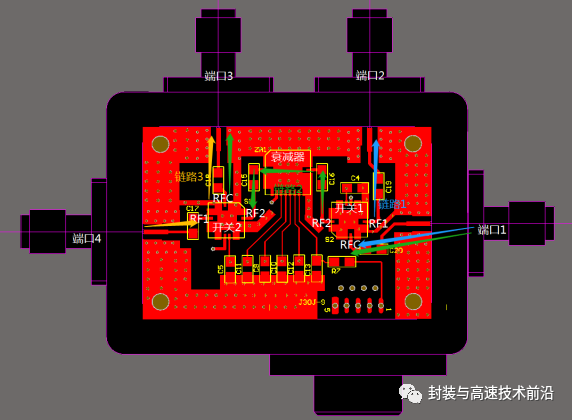

1. 该产品是一个射频系统中的校准模块,主要由两个射频开关、一个数控衰减器、四个端口以及若干阻容组成

2. 关注频段:X波段——8GHz~12GHz

3. 主要有3条传输链路,如下图,端口1-开关1-端口2的蓝色路径,端口4-开关2-端口3的黄色路径以及端口1-开关1-衰减器-开关2-端口3的绿色路径,由开关控制实现

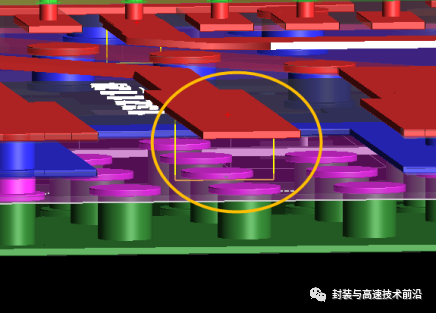

4. PCB层叠结构如下图,采用高频材料罗杰斯4350,针对射频性能优化的特殊工艺有:所有过孔填铜、整板镀金、不涂覆阻焊层。

问题描述:

实际测试PCB板加上外部结构件的插入损耗(衰减)与回波损耗时,开关选通不同通路时,回波损耗基本在-15dB左右,驻波满足要求。但是端口1到端口2的衰减与端口3到端口4的衰减达到了8dB左右,端口1到端口3的衰减更是达到了16dB,衰减过大,已经影响到系统的正常使用。

通过PCB板设计的排查,射频链路中的电容为0603封装,相比0402,焊盘处增加了阻抗不连续,而且0603封装比0402封装的寄生参数更大,对互连通道的影响更大;另外,地铜包裹处理不够好,整体链路的布局布线并没有做到短、直。这些设计的不当容易导致衰减的增大。

02

—

仿真思路

为了仿真分析不同射频链路的衰减及回波损耗情况,并验证优化方向,主要通过以下几个步骤实现:

1. 利用Cadence Sigrity 3DEM全波仿真模块对版图进行3D全波电磁场提取,得到版图的精确电磁场结果——S参数模型

主要过程:

2) 设置玻纤参数、铜皮蚀刻、铜皮粗糙度等参数(如有相关数据)

3) 除了4个端口port外,增加3个芯片的port5-12,提取3D全波的版图S参数模型。

4) 经过仿真计算后,查看3D mesh图和全波算法收敛的迭代图

5) 经过仿真计算后,PCB版图的S参数模型保存为.snp文件

2. 将开关、衰减器(器件商提供)和3D-EM提取的版图S参数模型带入Cadence Sigrity TopologyExplorer中进行联合S参数抽取,得到各种情况下的结果。

主要过程:

1) 搭建S参数的电路拓扑图

2) S参数拓扑提取

3. 因存在射频开关,需要根据开关控制分情况进行评估:

1) Case1:开关1选通RF1,开关1选用模型on(RFC-RF1)评估端口1到端口2的衰减,以及1和2端口的回波;开关2选通RF1,开关2选用模型on(RFC-RF1)评估端口4到端口3的衰减,以及3和4端口的回波

2) Case2:开关1选用模型off(RFC-RF1),开关2选用模型off(RFC-RF1),评估1和2端口、3和4端口之间的隔离度

3) Case3:开关1选用模型off(RFC-RF2),开关2选用模型on(RFC-RF2),评估1和3端口的隔离度

4) Case4:开关1选用模型on(RFC-RF2),开关2选用模型on(RFC-RF2),评估1到3端口的衰减

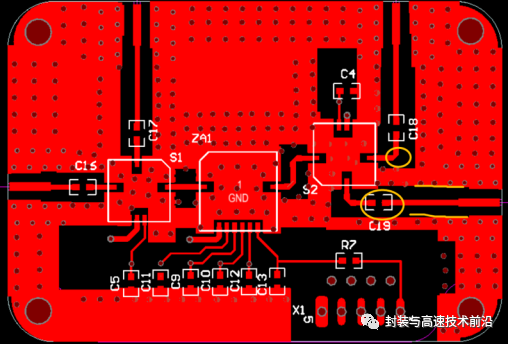

4. 改善PCB版图设计,重新仿真,优化点:

1) 0603电容改为0402

2) 优化45度走线,全部改为切角

3) 优化布局,使得链路尽量短、直

4) 射频主链路增加地铜包裹

03

—

仿真结果分析与结果

1. 原始设计

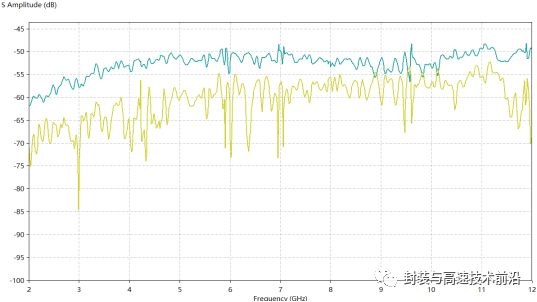

Case1的衰减如下图,从结果来看,X波段,端口1到端口2的衰减和端口3到端口4的衰减在6dB以下,对于如此短的链路,这么大的损耗需要对版图进行优化,而且与测试结果基本吻合,因为本仿真仅分析了PCB板,没有考虑结构件的影响。

Case1衰减

Case1的回波损耗如下图,X波段,Case1情况下都选通RF1时,4个端口的回波曲线如上图,基本都在-15dB以下,只有端口1差一些,差到-12dB左右。

Case1回波

Case2的隔离度如下图,绿色曲线为端口1与端口2之间的隔离度,黄色曲线为端口3与端口4之间的隔离度,X波段,端口1与端口2的隔离度大于48dB,端口3与端口4的隔离度大于52dB。

Case2隔离度

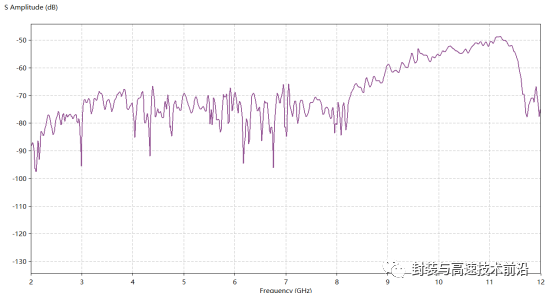

Case3的隔离度如下图,X波段,端口1与端口3的隔离度大于50dB,但满足不了60dB的要求,需要对版图进行优化。

Case3隔离度

Case4的衰减如下图,X波段,端口1到端口3的衰减达到14dB左右,与测试结果基本吻合。

Case4衰减

Case4的回波损耗如下图,X波段,端口1与端口3的回波损耗都在12dB以下。

Case4回波

2. 改善设计

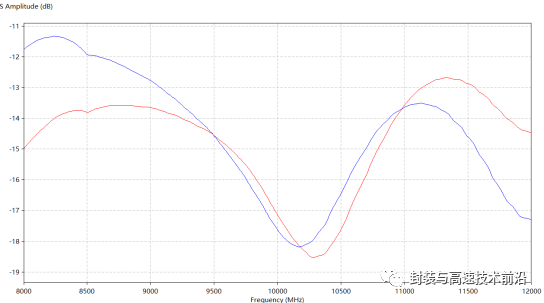

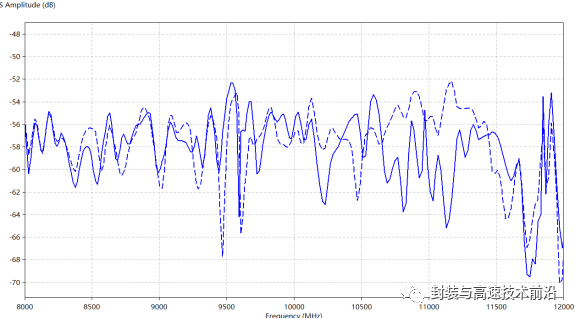

Case1的衰减对比如下图所示,红色实线为改善设计的端口1与端口2之间的衰减,红色虚线为原始设计端口1与2之间的衰减,蓝色实线为改善设计端口3与端口4之间的衰减,蓝色虚线为原始设计端口3与4之间的衰减,经过优化,1-2链路与3-4链路的衰减相比未优化前有了大幅提升,在X波段衰减均小于3dB

Case1原始设计与改善设计衰减对比

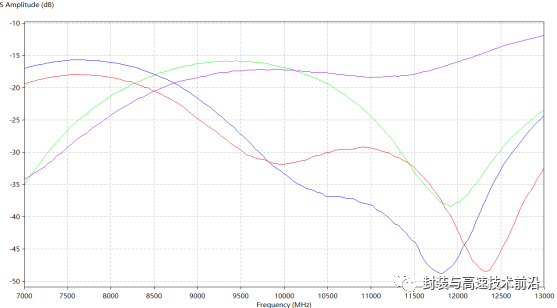

Case1的回波损耗如下图,红色为端口1,蓝色为端口2,绿色为端口3,紫色为端口4,回波均小于-15dB

Case1回波

Case1端口1的回波损耗对比如下图,红色实线为改善设计的端口1回损,虚线为原始版本的端口1回损,与原始设计相比,端口回波也有较大的提升。

Case1端口1原始设计与改善设计回波对比

Case2的端口1-2隔离度如下图,红色实线为改善设计的隔离度,虚线为原始设计的隔离度,优化过后,端口1-2的隔离度普遍提升了3dB以上

Case2端口1-2原始设计与改善设计隔离度对比

Case2的端口3-4隔离度如下图,蓝色实线为改善设计的隔离度,虚线为原始设计的隔离度,优化前后隔离度相差不大,均满足要求

Case2端口3-4原始设计与改善设计隔离度对比

Case3的端口1-3隔离度如下图,红色实线为改善设计的隔离度,虚线为原始设计的隔离度,优化过后,端口1-3的隔离度大大提升,由之前的50dB改善到60dB

Case3端口1-3原始设计与改善设计隔离度对比

Case4的衰减对比如下图,红色实线为改善设计的衰减,虚线为原始设计的衰减,优化过后,端口1-3链路的衰减大大降低,基本全X波段在8dB以下

Case4原始设计与改善设计衰减对比

Case4的回波如下图,红色为端口1的回波损耗,蓝色为端口3的回波损耗,回波基本都在-12dB以下,满足要求

Case4回波

3. 因此通过合适的版图设计优化,大大降低了射频链路的衰减,使得端口1-2链路、端口3-4链路的衰减均小于3dB,端口1-3链路的衰减小于8dB;端口回损也得到了一定程度的提升;端口之间的隔离度也得到了优化,端口1、2之间和端口3、4之间的隔离度在满足要求的前提下得到了进一步地增大,端口1、3之间的隔离度则是大大提升,满足要求。

04

—

结论

本次案例利用Cadence的Sigrity 3DEM与TopologyExplorer对射频模块PCB板进行了3D全波的电磁场建模,成功地对测试中的问题进行了复现,并通过设计仿真迭代,给出了改善方案,最终解决了射频模块的问题,改板后系统可以正常工作。

更多技术文章与讨论欢迎关注微信公众号:

封装与高速技术前沿

微信号 : APDtech